# EFFICIENT TRANSMITTER/RECEIVER ARCHITECTURES FOR HIGH PERFORMANCE WIRELESS APPLICATIONS

A thesis submitted by

## SHAHANA T. K.

for the award of the degree of

## DOCTOR OF PHILOSOPHY

Under the guidance of

Dr. K. POULOSE JACOB and Dr. SREELA SASI

# DEPARTMENT OF COMPUTER SCIENCE FACULTY OF TECHNOLOGY COCHIN UNIVERSITY OF SCIENCE AND TECHNOLOGY KOCHI 682 022, INDIA

OCTOBER 2008

# EFFICIENT TRANSMITTER/RECEIVER ARCHITECTURES FOR HIGH PERFORMANCE WIRELESS APPLICATIONS

### Ph. D. Thesis in the field of Wireless Communication

## Author

Shahana T.K. Research Scholar Department of Computer Science Cochin University of Science and Technology Kochi – 682 022, Kerala, India E-mail: shahanatk@cusat.ac.in

## **Reseach Advisors**

#### Dr. K. Poulose Jacob

Professor and Head Department of Computer Science Cochin University of Science and Technology Kochi – 682 022, Kerala, India E-mail: kpj@cusat.ac.in

#### Dr. Sreela Sasi

Associate Professor Department of Computer & Information Science Gannon University PA, USA E-mail: sasi001@gannon.edu

October 2008

### CERTIFICATE

This is to certify that this thesis entitled "EFFICIENT TRANSMITTER/RECEIVER ARCHITECTURES FOR HIGH PERFORMANCE WIRELESS APPLICATIONS" is a bonafide record of the research work carried out by Ms. Shahana T. K. under my supervision and guidance in the Department of Computer Science, Cochin University of Science and Technology with Dr. Sreela Sasi, Associate Professor, Gannon University, PA, USA as co-guide. The results presented in this thesis or parts of it have not been presented for the award of any other degree.

30<sup>th</sup> October 2008

Dr. K. POULOSE JACOB (Supervising Guide) Professor and Head Department of Computer Science Cochin University of Science and Technology Kochi-682 022, Kerala.

#### CERTIFICATE

This is to certify that this thesis entitled "EFFICIENT TRANSMITTER/RECEIVER ARCHITECTURES FOR HIGH PERFORMANCE WIRELESS APPLICATIONS" is a bonafide record of the research work carried out by Ms. Shahana T. K. under the supervision and guidance of Dr. K. Poulose Jacob, Professor and Head, Department of Computer Science, Cochin University of Science and Technology with myself as co-guide. The results presented in this thesis or parts of it have not been presented for the award of any other degree.

Nulabari

30<sup>th</sup> October 2008

Dr. SREELA SASI Associate Professor Department of Computer & Information Science Gannon University, PA, USA.

#### **DECLARATION**

I hereby declare that the work presented in this thesis entitled "EFFICIENT TRANSMITTER/RECEIVER ARCHITECTURES FOR HIGH PERFORMANCE WIRELESS APPLICATIONS" is based on the original research work carried out by me under the supervision and guidance of Dr. K. Poulose Jacob, Professor and Head, Department of Computer Science, Cochin University of Science and Technology with Dr. Sreela Sasi, Associate Professor, Department of Computer and Information Science, Gannon University, PA, USA as co-guide. The results presented in this thesis or parts of it have not been presented for the award of any other degree.

SHAHANA T. K.

Kochi - 682 022 30<sup>th</sup> October 2008

#### ACKNOWLEDGEMENT

I am deeply indebted and grateful to many people who supported me during the research work and preparation of the thesis.

First and foremost, I give special thanks and glory to the God Almighty for giving me the grace, wisdom and health to complete this endeavour.

I would like to express sincere gratitude and appreciation to my supervising guide Dr. K. Poulose Jacob, Professor and Head, Department of Computer Science, Cochin University of Science and Technology for his constant encouragement, support and guidance. His sincerity, positive and supportive attitude, calmness and scholarly advice have been a steady source of inspiration to me.

My deepest gratitude and respect also goes to Dr. Sreela Sasi for her guidance and assistance as co-supervisor. Her creative comments and suggestions from the initial conception to the end of this work are highly appreciated. I am greatly indebted to her for financial assistance which enabled me to register for several international conferences abroad, and also for endless hours of help for reviewing the research papers and the thesis.

I am highly indebted and grateful to Dr. Jimson Mathew, Department of Computer Science, University of Bristol, UK, for his tremendous support and encouragement. Special thanks to him for his patient listening to my questions, giving necessary reference materials and constructive comments which helped a lot to keep me on track.

I am thankful to Dr. R. Gopikakumari, Division Head, and all my colleagues at the Division of Electronics and Communication Engineering, School of Engineering, Cochin University of Science and Technology for their encouragement and support.

I am very grateful to Anju Pradeep, Babita R Jose, Mridula S., Rekha K. James and Sheena Mathew for their friendship, cooperation, support and care which helped me to endure this program.

I appreciate the technical and non-technical staff of the Department of Computer Science, Cochin University of Science and Technology for their timely help.

I owe heartfelt thanks to my parents and my mother-in-law for their motivation, encouragement and understanding when it was mostly required. Also, I remember my sisters with gratitude for their affectionate support.

A special mention to my husband Zakir, and my children Tasneem and Hasna for their love, understanding and support.

#### SHAHANA T. K.

### ABSTRACT

Wireless communication has become an integral part of modern society with an ultimate aim of global roaming. The developments in satellite transmission, radio and television broadcasting, and the new generation mobile systems have revolutionized global communication. The recent trend in wireless communication is to implement a single transceiver hardware platform that can support multiple communication standards. The progress in CMOS technology opens opportunities to implement flexible platforms at low cost and low power. In this research, analysis has been done on architectures and design techniques that enhances integration and programmability of RF transceivers for wireless communication; and compact, inexpensive, low power communication devices that are robust, testable and capable of handling multiple standards have been developed.

The thesis focuses on the development of reconfigurable architectures and high performance building blocks suitable for wireless communication. For efficient multi-mode operation, advanced analog-to-digital converter (ADC) solutions are required with flexibility to adapt to the bandwidth and speed of the high data rate standards. Sigma-delta ADC is the most promising solution to achieve high resolution over a wide variety of bandwidth requirements. The most complex part of a sigma-delta ADC is the digital decimation filter. So, efficient, high speed and reconfigurable implementation of decimation filter is a key to achieve high performance. The main objectives of the research are to:

• Reduce the complexity of decimation filter design by developing a toolbox

- Design Residue Number System (RNS) based dual-mode decimation filters for high speed, small die area and low power operation

- Reduce the complexity of RNS conversion circuitry

- Improve the performance of the communication system through an efficient concatenated coding scheme

- Realize easily testable circuits using Reed-Muller (RM) logic

The major achievements in this research are the following:

- A decimation filter design toolbox is developed in MALAB<sup>®</sup> Graphical User Interface Development Environment (GUIDE) which enables the user to perform quick filter design and analysis for six popular wireless standards.

- A reconfigurable RNS based decimation filter is designed and implemented for WCDMA/WiMAX and WCDMA/WLAN dual-mode operation. The performance analysis shows that it has high speed, less area and low power dissipation compared to the implementation in traditional binary number system.

- A direct analog-to-residue converter based on sigma-delta ADC is designed to reduce the complexity of RNS conversion circuitry. It has high resolution, high conversion speed, medium hardware complexity and low cost of implementation compared to the existing Nyquist rate converters.

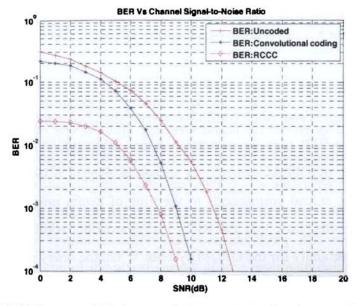

- An Orthogonal Frequency Division Multiplexing (OFDM) based communication system is simulated using a novel Redundant Residue Number System (RRNS) – Convolutional concatenated coding

scheme. This coding scheme offers significant improvements in bit error rate (BER) under different operating conditions.

• Easily testable circuit realization for multiply and accumulate units of the filter is achieved by implementing in RM form. New algorithms for combinational logic synthesis in RM form are also developed using exhaustive branching and genetic algorithm based approaches.

The performance evaluations show that these efficient design methods and reconfigurable implementations in RNS domain yield high speed operation in addition to reduction in area and power consumption. Also, the direct analog-to-residue conversion technique reduced the overall hardware complexity. The RRNS-convolutional concatenated coding designed for forward error correction in an OFDM communication system achieved significant BER improvement. Hence these design techniques and circuits are dependable alternatives that could be used for high performance wireless applications.

## CONTENTS

|       |                                                    |                                                  | Page No. |

|-------|----------------------------------------------------|--------------------------------------------------|----------|

| LIST  | of figur                                           | RES                                              | v        |

| LIST  | OF TABLE                                           | ES                                               | ix       |

| LIST  |                                                    | EVIATIONS                                        | xi       |

|       |                                                    |                                                  |          |

| Chap  | ter 1                                              |                                                  |          |

| INTRO | ODUCTIO                                            | Ν                                                | 1        |

| 1.1   | History                                            | of Wireless Communication                        | 3        |

| 1.2   | Wireles                                            | ss System Developments                           | 5        |

| 1.3   | Conver                                             | ntional RF Receiver Architectures                | 5        |

|       | 1.3.1                                              | Superheterodyne Receiver                         | 6        |

|       | 1.3.2                                              | Direct Conversion Homodyne Receiver              | 7        |

|       | 1.3.3                                              | Low IF Receiver                                  | 8        |

|       | 1.3.4                                              | Wideband IF Double Conversion Receiver           | 8        |

| 1.4   | Analog                                             | -to-Digital Converters                           | 9        |

|       | 1.4.1                                              | Nyquist Rate Analog-to-Digital Converters        | 10       |

|       | 1.4.2                                              | Oversampling Analog-to-Digital Converters        | 10       |

|       |                                                    | 1.4.2.1 Sigma-Delta Analog-to-Digital Converters | 12       |

| 1.5   | Layout                                             | of the Thesis                                    | 14       |

|       |                                                    |                                                  |          |

| Chap  | ter 2                                              |                                                  |          |

| DECI  | MATION F                                           | ILTER DESIGN: A TOOLBOX APPROACH                 | 17       |

| 2.1   | Decima                                             | ation Filter Design Considerations               | 19       |

| 2.2   | Receive                                            | er Architecture for Multi-standard operation     | 21       |

|       | 2.2.1                                              | Reconfigurable Sigma-Delta ADC                   | 22       |

| 2.3   | Multista                                           | age Decimation Filter                            | 24       |

|       | 2.3.1                                              | Cascaded Integrator Comb Filter                  | 26       |

|       | 2.3.2                                              | Halfband Filter                                  | 28       |

|       | 2.3.3                                              | FIR Filter                                       | 29       |

| 2.4   | Decima                                             | ation Filter Design Specification                | 30       |

| 2.5   | Multi-standard Decimation Filter Design Toolbox 32 |                                                  |          |

| 2.6  | Polyph  | Polyphase Implementation of Non-recursive Comb Decimators       |                                      |    |  |  |

|------|---------|-----------------------------------------------------------------|--------------------------------------|----|--|--|

|      | 2.6.1   | Classica                                                        | I Recursive CIC Filter               | 42 |  |  |

|      | 2.6.2   | Non-reci                                                        | ursive CIC Filter                    | 43 |  |  |

|      | 2.6.3   | Polypha                                                         | se Non-recursive CIC Architecture    | 44 |  |  |

|      | 2.7     | Summar                                                          | у                                    | 47 |  |  |

| Chap | iter 3  |                                                                 |                                      |    |  |  |

| RNS  | BASED P | ROGRAMM                                                         | ABLE MULTI-MODE DECIMATION FILTERS   | 49 |  |  |

| 3.1  | Residu  | e Number S                                                      | System                               | 51 |  |  |

|      | 3.1.1   | RNS Bas                                                         | sics                                 | 51 |  |  |

|      | 3.1.2   | RNS Arit                                                        | thmetic                              | 52 |  |  |

|      | 3.1.3   | Forward                                                         | and Reverse Conversions              | 53 |  |  |

|      | 3.1.4   | Choice o                                                        | Choice of RNS Moduli                 |    |  |  |

| 3.2  | FIR Di  | FIR Digital Filter Design: RNS Versus Traditional               |                                      |    |  |  |

|      | 3.2.1   | FIR Filter                                                      | r Architecture                       | 57 |  |  |

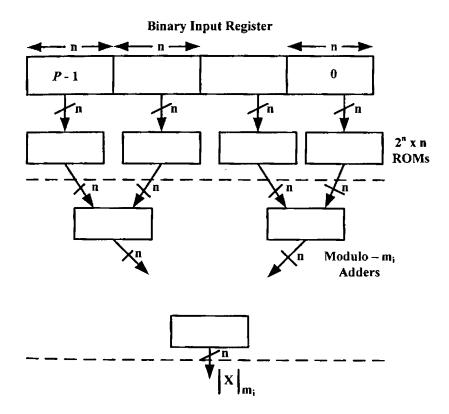

|      |         | 3.2.1.1                                                         | Forward Converter                    | 58 |  |  |

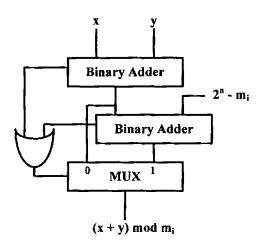

|      |         | 3.2.1.2                                                         | Modulo Addition                      | 59 |  |  |

|      |         | 3.2.1.3                                                         | Modulo Multiplication                | 60 |  |  |

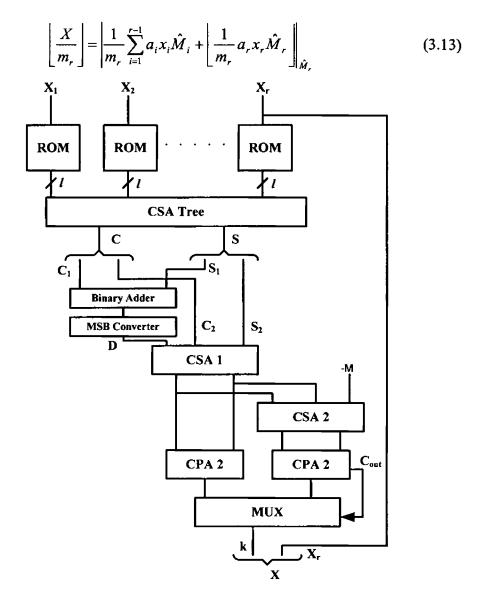

|      |         | 3.2.1.4                                                         | Reverse Converter                    | 61 |  |  |

| 3.3  | RNS b   | RNS based Dual-mode Decimation Filters                          |                                      |    |  |  |

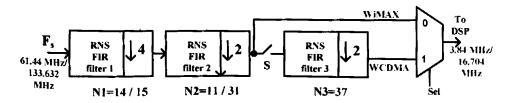

|      | 3.3.1   | Rceceive                                                        | 65                                   |    |  |  |

|      | 3.3.2   | Duai-moo                                                        | de Decimation Filter for WCDMA/WiMAX | 65 |  |  |

|      |         | 3.3.2.1                                                         | Design Considerations                | 66 |  |  |

|      | 3.3.3   | Dual-mod                                                        | de Decimation Filter for WCDMA/WLANa | 69 |  |  |

|      |         | 3.3.3.1                                                         | Design Considerations                | 70 |  |  |

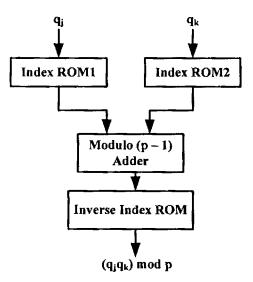

| 3.4  | RNS M   | ultiplier usin                                                  | g Index Calculus                     | 72 |  |  |

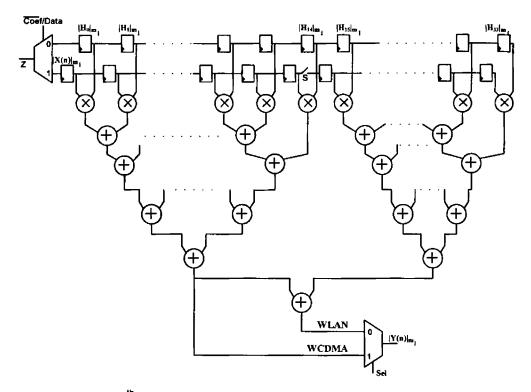

| 3.5  | Program | Programmable Decimation Filter using Index Calculus Multipliers |                                      |    |  |  |

|      | 3.5.1   | Design C                                                        | considerations                       | 75 |  |  |

| 3.6  | Summa   | ry 7                                                            |                                      |    |  |  |

Chapter 4

| RRNS-C  | ONVOLU        | TIONAL                                                                  | CONCA       | <b>FENATED</b>  | CODE      | 0 (              | FDM    | WIRELESS       | 81  |

|---------|---------------|-------------------------------------------------------------------------|-------------|-----------------|-----------|------------------|--------|----------------|-----|

| COMMU   | INICATIO      | N SYSTEM                                                                | WITH A DI   | RECT ANALO      | G-TO-RI   | esidue           | CON    | VERTER         |     |

| 4.1     | Direct An     | Direct Analog-to-Residue Converters                                     |             |                 |           |                  |        | 83             |     |

|         | 4.1.1         | Nyquist Rat                                                             | e Analog-to | -Residue Con    | verters   |                  |        |                | 83  |

|         |               | 4.1.1.1                                                                 | Multiple-R  | esidue Flash A  | VR Conv   | erter            |        |                | 84  |

|         |               | 4.1.1.2                                                                 | Successiv   | e Approximatio  | on based  | A/R Col          | nverte | er             | 86  |

|         |               | 4.1.1.3                                                                 | Iterative S | ubranging Flas  | sh A/R C  | onvert <b>er</b> |        |                | 87  |

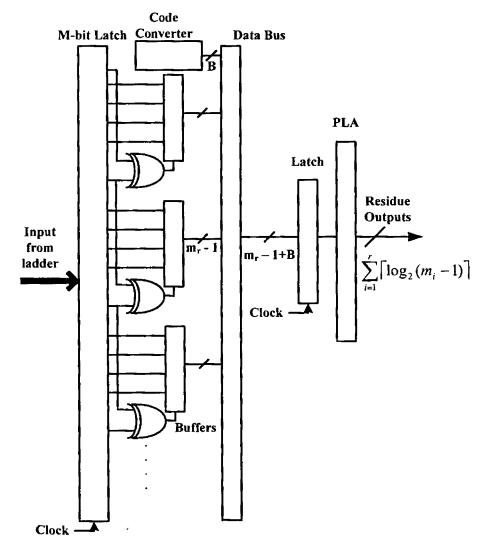

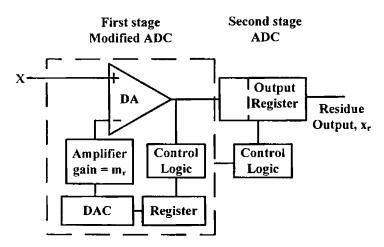

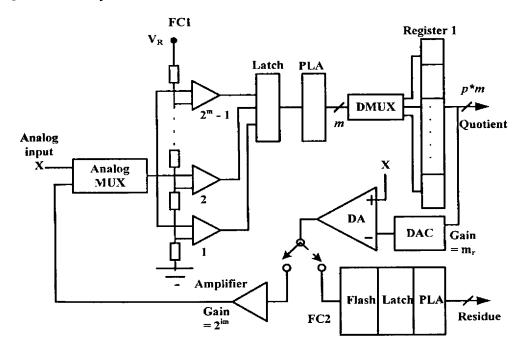

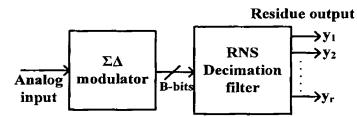

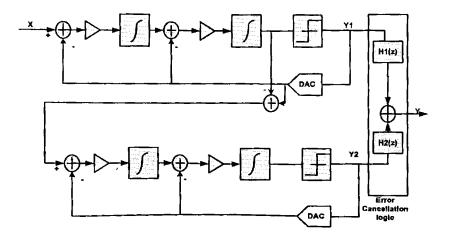

|         | 4.1.2         | A Novel Sig                                                             | ma-Delta b  | ased parallel A | Analog-to | -Residu          | e Cor  | verter         | 90  |

|         |               | 4.1.2.1                                                                 | Sigma-De    | Ita Modulator   |           |                  |        |                | 90  |

|         |               | 4.1.2.2                                                                 | RNS base    | d Decimation F  | Filter    |                  |        |                | 92  |

| 4.2     | RRNS-C        | onvolutional                                                            | encoded     | Concatenated    | Code      | for Of           | DM     | based wireless | 94  |

|         | Communication |                                                                         |             |                 |           |                  |        |                |     |

|         | 4.2.1         | OFDM Communication System                                               |             |                 |           |                  | 95     |                |     |

|         | 4.2.2         | Error Detection and Correction with RRNS                                |             |                 |           |                  | 97     |                |     |

|         | 4.2.3         | System Description                                                      |             |                 |           |                  | 100    |                |     |

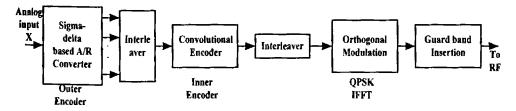

|         |               | 4.2.3.1                                                                 | Transmitte  | er Model        |           |                  |        |                | 101 |

|         |               | 4.2.3.2                                                                 | Receiver I  | Model           |           |                  |        |                | 102 |

| 4.3     | Summary       | /                                                                       |             |                 |           |                  |        |                | 105 |

|         |               |                                                                         |             |                 |           |                  |        |                |     |

| Chapter |               |                                                                         |             |                 |           |                  |        |                |     |

| EASILY  | TESTAB        | LE CIRCUIT                                                              | S FOR MA    | CUNITS          |           |                  |        |                | 107 |

| 5.1     | Reed-Mu       | iller Expressi                                                          | ons         |                 |           |                  |        |                | 109 |

| 5.2     | Easily Te     | stable Circui                                                           | ts          |                 |           |                  |        |                | 112 |

| 5.3     |               | Combinational Logic Synthesis using Reed-Muller Universal Logic Modules |             |                 |           |                  | 113    |                |     |

|         | 5.3.1         | N-ary Exha                                                              | ustive Bran | ching Techniqi  | Je        |                  |        |                | 115 |

|         | 5.3.2         | Exhaustive                                                              | Branching   | Algorithm       |           |                  |        |                | 117 |

| 5.4     |               | Algorithm bas                                                           | sed Approa  | ch for Combin   | ational L | ogic Syn         | thesis | 6              | 119 |

|         | 5.4.1         | Universal Lo                                                            | ogic Module | es for Logic Sy | nthesis   |                  |        |                | 120 |

|         | 5.4.2         | GA based A                                                              | pproach fo  | or Logic Synthe | sis       |                  |        |                | 121 |

5.5 Summary

124

#### Chapter 6

INDEX

| SIMUL  | ATION R                                                                          | ESULTS AND ANALYSIS                                                         | 127 |  |  |  |  |

|--------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|--|--|--|--|

| 6.1    | Decima                                                                           | tion Filter Implementation and Analysis                                     | 129 |  |  |  |  |

| 6.2    | Simulat                                                                          | ion Results and Analysis of Polyphase Non-recursive Comb Decimation Filter  | 131 |  |  |  |  |

| 6.3    | Perform                                                                          | nance Analysis of FIR Filter Implementation: RNS Versus Traditional         | 135 |  |  |  |  |

| 6.4    | Simulation Results and Analysis of Dual-mode Decimation Filter for WCDMA/WiMAX 1 |                                                                             |     |  |  |  |  |

| 6.5    | Simulat                                                                          | ion Results and Analysis of Dual-mode Decimation Filter for WCDMA/WLANa     | 144 |  |  |  |  |

| 6.6    | Implem                                                                           | entation of Programmable Decimation Filter using Index Calculus Multipliers | 146 |  |  |  |  |

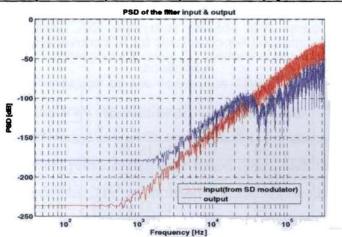

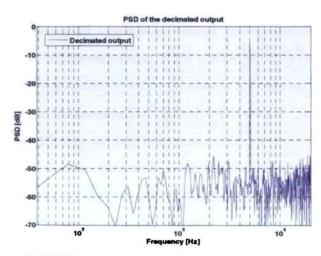

| 6.7    | Simulat                                                                          | ion Results for Sigma-Delta based Parallel Analog-to-Residue Converter      | 150 |  |  |  |  |

| 6.8    | Simulat                                                                          | ion Results and Performance Analysis of RRNS-Convolutional Concatenated     | 154 |  |  |  |  |

|        | Coding                                                                           | for OFDM System                                                             |     |  |  |  |  |

|        | 6.8.1                                                                            | Additive White Gaussian Noise Tolerance                                     | 154 |  |  |  |  |

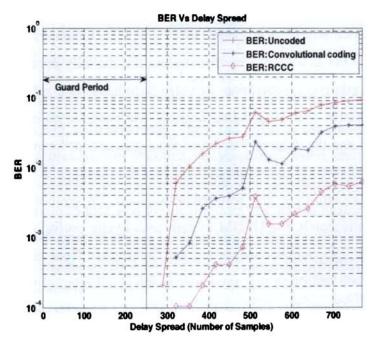

|        | 6.8.2                                                                            | Multipath Delay Spread Immunity                                             | 155 |  |  |  |  |

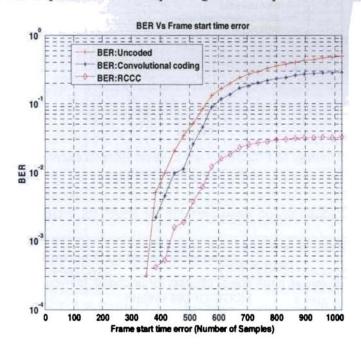

|        | 6.8.3                                                                            | Effects of Frame Synchronization Errors                                     | 157 |  |  |  |  |

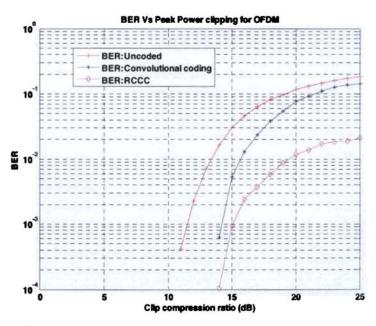

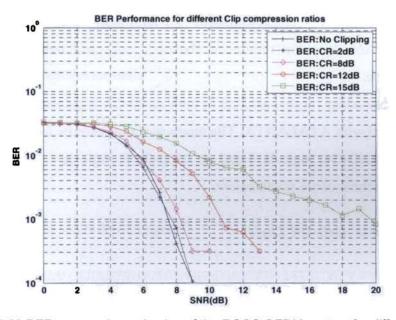

|        | 6.8.4                                                                            | Peak Power Clipping for PAPR Reduction                                      | 158 |  |  |  |  |

| 6.9    | Simulat                                                                          | ion Results for Easily Testable MAC Units                                   | 160 |  |  |  |  |

| 6.10   | Combin                                                                           | national Logic Synthesis Results using Exhaustive Branching Algorithm       | 163 |  |  |  |  |

| 6.11   | GA bas                                                                           | ed Combinational Logic Synthesis Results using ULMs                         | 167 |  |  |  |  |

| 6.12   | Summa                                                                            | ary                                                                         | 172 |  |  |  |  |

| Chapt  | er 7                                                                             |                                                                             |     |  |  |  |  |

| CONC   | LUSIONS                                                                          | AND SUGGESTIONS FOR FURTHER WORK                                            | 175 |  |  |  |  |

| 7.1    | Conclu                                                                           | sions                                                                       | 177 |  |  |  |  |

| 7.2    | Sugges                                                                           | tions for Further Work                                                      | 179 |  |  |  |  |

| REFE   | RENCES                                                                           |                                                                             | 181 |  |  |  |  |

| LIST ( | OF PUBLI                                                                         | CATIONS OF THE AUTHOR                                                       | 195 |  |  |  |  |

199

iv

## LIST OF FIGURES

| Figure 1.1  | Block diagram of a RF Transceiver                                                       | 6  |

|-------------|-----------------------------------------------------------------------------------------|----|

| Figure 1.2  | Superheterodyne receiver                                                                | 7  |

| Figure 1.3  | Direct conversion homodyne receiver                                                     | 8  |

| Figure 1.4  | Low IF receiver                                                                         | 8  |

| Figure 1.5  | Wideband IF double conversion receiver                                                  | 9  |

| Figure 1.6  | Block diagram of analog-to-digital converter                                            | 9  |

| Figure 1.7  | Baseband quantization noise power                                                       | 12 |

| Figure 1.8  | Block diagram of first order sigma-delta ADC                                            | 12 |

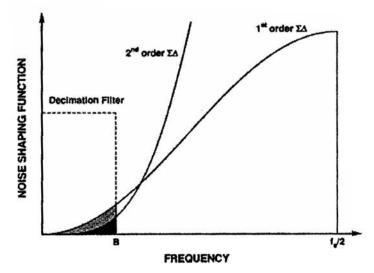

| Figure 1.9  | Noise shaping in sigma-delta modulators                                                 | 14 |

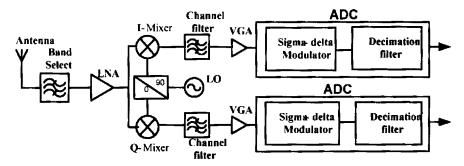

| Figure 2.1  | Direct conversion homodyne receiver architecture                                        | 22 |

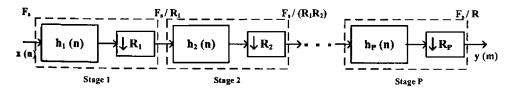

| Figure 2.2  | Multistage decimation filter                                                            | 25 |

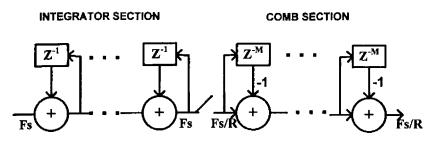

| Figure 2.3  | CIC decimation filter                                                                   | 27 |

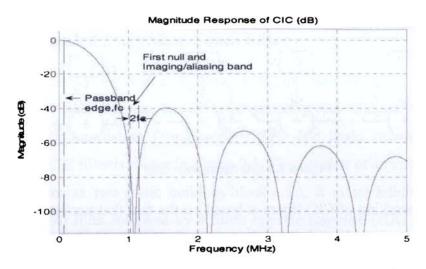

| Figure 2.4  | CIC magnitude response for GSM with $F_s$ = 34.667MHz, R = 32, M = 1 and k = 3          | 28 |

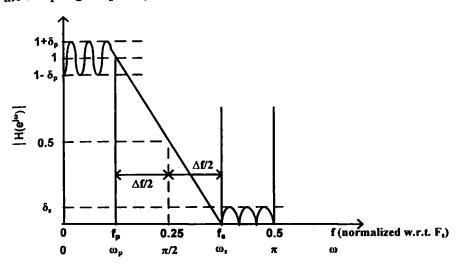

| Figure 2.5  | Magnitude response of halfband filter                                                   | 29 |

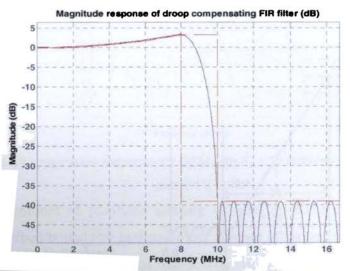

| Figure 2.6  | Magnitude response of droop compensating FIR filter with $M = 1$ and $k = 4$            | 30 |

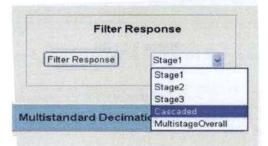

| Figure 2.7  | GUI for Multi-standard Decimation Filter Design Toolboox                                | 33 |

| Figure 2.8  | Pop-up menu for standard selection                                                      | 33 |

| Figure 2.9  | Decimation filter details for GSM                                                       | 33 |

| Figure 2.10 | Cost of decimation filter implementation for GSM                                        | 34 |

| Figure 2.11 | Message box displaying filter coefficients for GSM                                      | 34 |

| Figure 2.12 | Pop-up menu for magnitude response selection                                            | 35 |

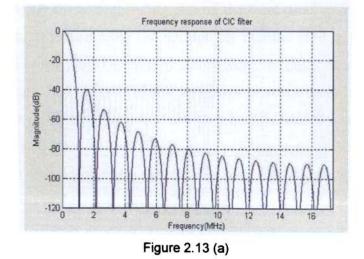

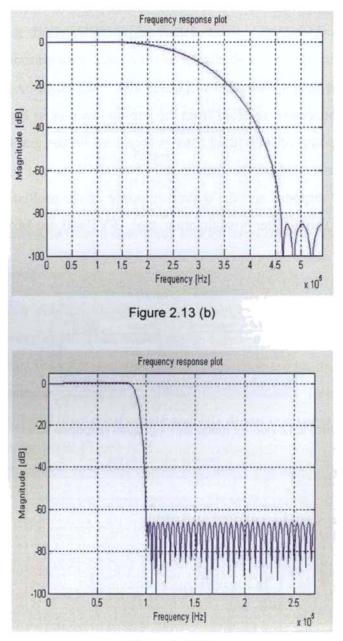

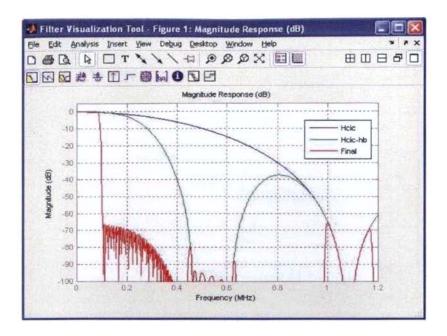

| Figure 2.13 | Individual Filter response for GSM displayed on front panel of GUI (a) CIC filter       | 36 |

|             | (b) Halfband filter (c) FIR filter                                                      |    |

| Figure 2.14 | Display of the cascaded filter response                                                 | 37 |

| Figure 2.15 | Pop-up menu for pole-zero plots                                                         | 38 |

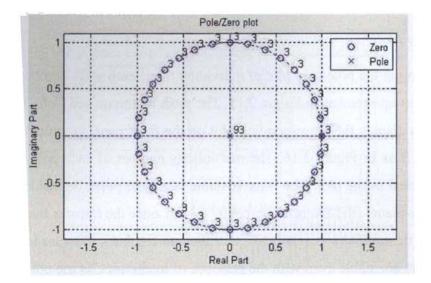

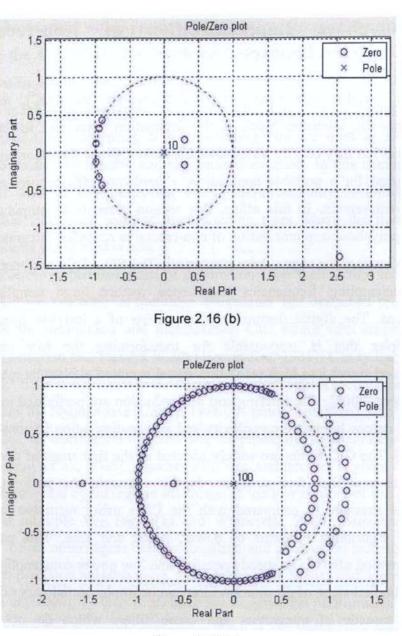

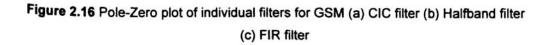

| Figure 2.16 | Pole-Zero plot of individual filters for GSM (a) CIC filter (b) Halfband filter (c) FIR | 39 |

|             | filter                                                                                  |    |

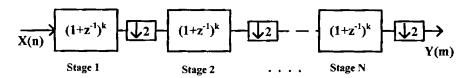

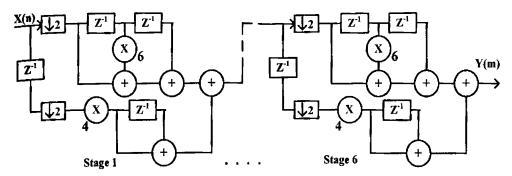

| Figure 2.17 | Non-recursive comb decimator                                                            | 44 |

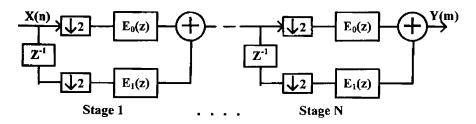

| Figure 2.18 | Polyphase realization of non-recursive comb decimator                                   | 45 |

| Figure 2.19 | Polyphase realization of non-recursive comb decimator for R = 64, k = 4                 | 47 |

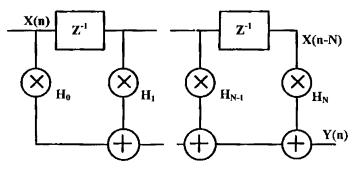

| Figure 3.1  | Traditional FIR filter architecture                                                     | 57 |

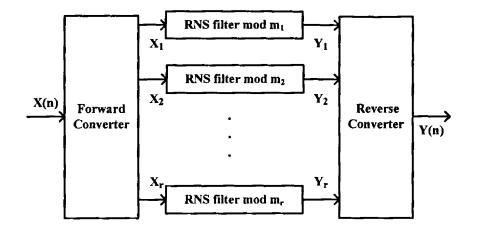

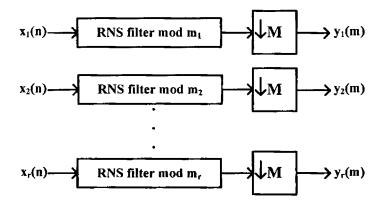

| Figure 3.2  | RNS implementation of FIR filter                                      | 58  |

|-------------|-----------------------------------------------------------------------|-----|

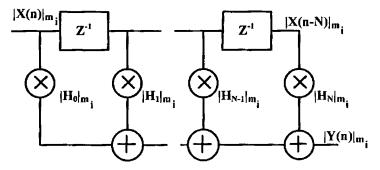

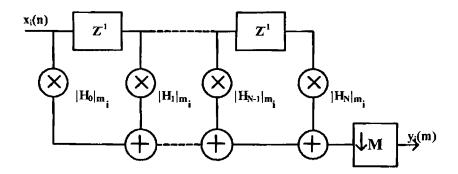

| Figure 3.3  | i <sup>th</sup> modulo filter channel                                 | 58  |

| Figure 3.4  | Forward conversion logic for $\left X ight _{m_i}$                    | 59  |

| Figure 3.5  | Modulo adder                                                          | 60  |

| Figure 3.6  | Hardware efficient reverse converter                                  | 62  |

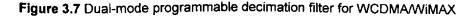

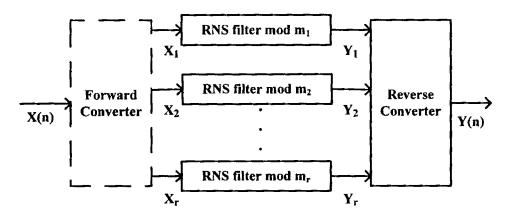

| Figure 3.7  | Dual-mode programmable decimation filter for WCDMA/WiMAX              | 67  |

| Figure 3.8  | RNS based FIR filter                                                  | 68  |

| Figure 3.9  | ith filter channel of stage 1 for WCDMA/WiMAX decimator               | 69  |

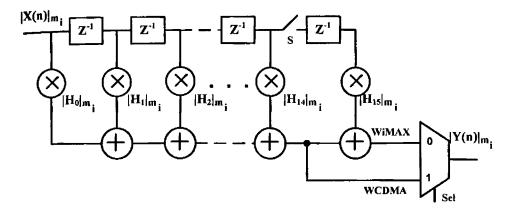

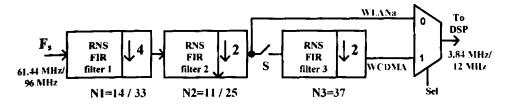

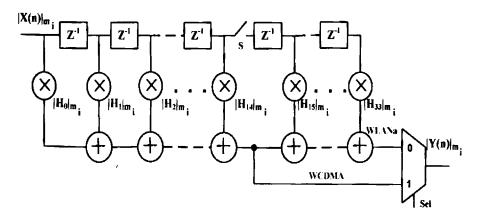

| Figure 3.10 | Dual-mode programmable decimation filter for WCDMA/WLANa              | 71  |

| Figure 3.11 | ith filter channel of stage 1 for WCDMA/WLANa decimator               | 71  |

| Figure 3.12 | Index calculus multiplier                                             | 73  |

| Figure 3.13 | ith filter channel of stage 1 programmable for WCDMA/WLANa            | 76  |

| Figure 4.1  | Multiple-residue flash converter                                      | 85  |

| Figure 4.2  | Successive approximation A/R converter                                | 87  |

| Figure 4.3  | Iterative flash A/R converter                                         | 89  |

| Figure 4.4  | Sigma-delta based parallel A/R converter                              | 90  |

| Figure 4.5  | A 2-2 cascaded MASH architecture                                      | 91  |

| Figure 4.6  | RNS based decimation filter for A/R converter                         | 93  |

| Figure 4.7  | ith modulo filter channel for A/R converter                           | 93  |

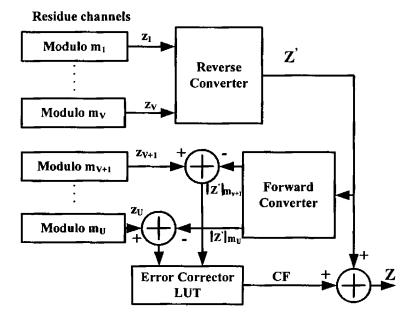

| Figure 4.8  | Principle of error correction with RRNS                               | 100 |

| Figure 4.9  | Block diagram of transmitter section                                  | 101 |

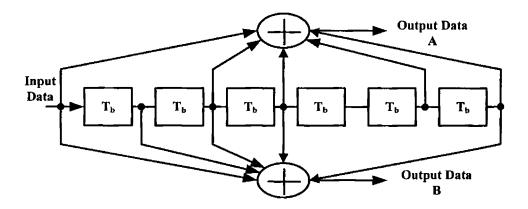

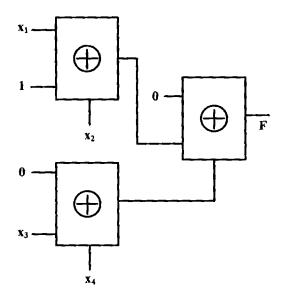

| Figure 4.10 | Convolutional encoder                                                 | 102 |

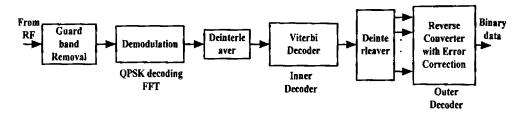

| Figure 4.11 | Block diagram of receiver section                                     | 104 |

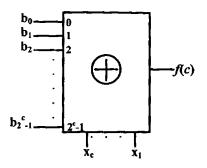

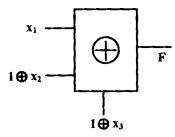

| Figure 5.1  | Logic symbol of RM-ULM(c)                                             | 114 |

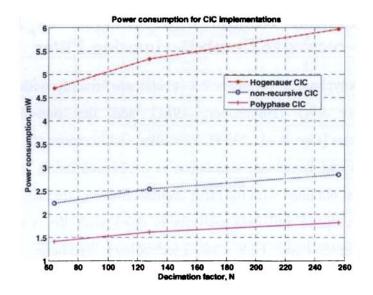

| Figure 6.1  | Power consumption for CIC architectures with $k = 4$ and $B_{in} = 4$ | 132 |

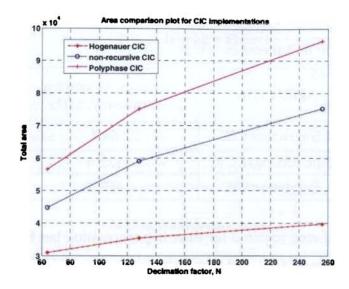

| Figure 6.2  | Area requirement for CIC architectures with $k = 4$ and $B_{in} = 4$  | 134 |

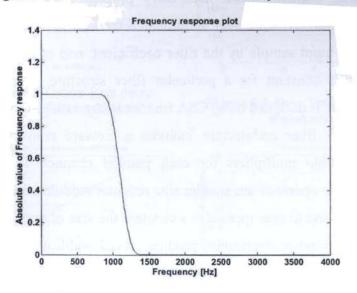

| Figure 6.3  | Frequency response of FIR filter                                      | 135 |

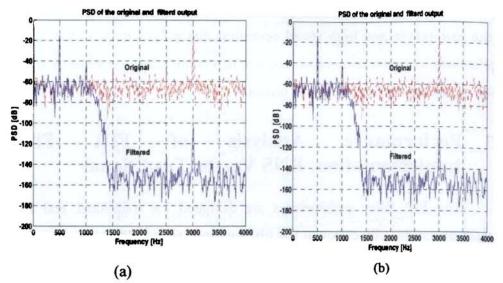

| Figure 6.4  | PSD plot of original and filtered output (a) Traditional (b) RNS      | 136 |

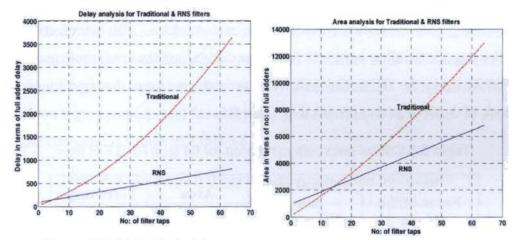

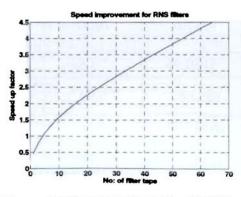

| Figure 6.5  | Critical Path delay: Traditional Vs RNS implementation                | 137 |

| Figure 6.6  | Area: Traditional Vs RNS implementation                               | 137 |

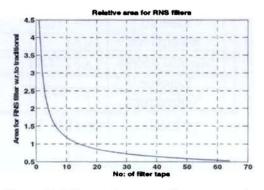

| Figure 6.7  | Speed up factor for RNS filter Vs traditional filter                  | 137 |

|             |                                                                       |     |

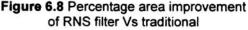

| Figure 6.8  | Percentage area improvement of RNS filter vs. traditional                         | 137 |

|-------------|-----------------------------------------------------------------------------------|-----|

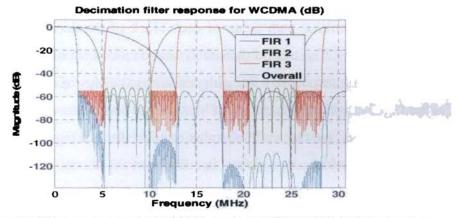

| Figure 6.9  | Filter responses for WCDMA mode in WCDMA/WiMAX decimator                          | 141 |

| Figure 6.10 | Filter responses for WiMAX mode in WCDMA/WiMAX decimator                          | 141 |

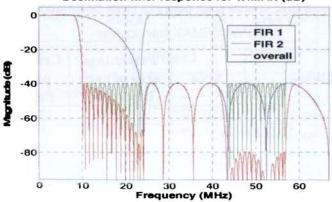

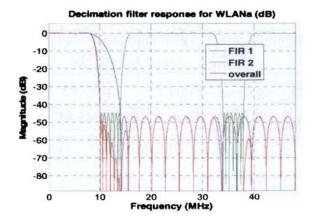

| Figure 6.11 | Filter responses for WCDMA mode in WCDMA/WLANa decimator                          | 144 |

| Figure 6.12 | Filter responses for WLANa mode in WCDMA/WLANa decimator                          | 144 |

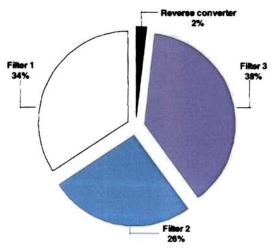

| Figure 6.13 | Area requirements for RNS decimation filter                                       | 147 |

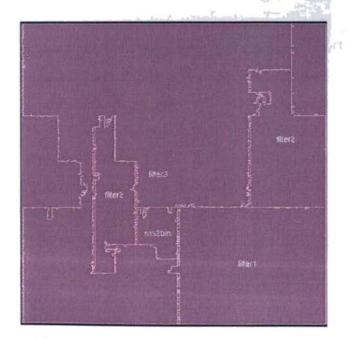

| Figure 6.14 | Placed cell structure for RNS based decimation filter                             | 149 |

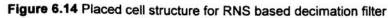

| Figure 6.15 | Routed view of RNS decimation filter                                              | 150 |

| Figure 6.16 | Power spectral density (PSD) plot for filter input and output                     | 151 |

| Figure 6.17 | PSD plot for decimation filter output at Nyquist rate                             | 151 |

| Figure 6.18 | BER versus SNR for uncoded, convolutional coded and RCCC OFDM system              | 155 |

| Figure 6.19 | BER versus multipath delay spread for uncoded, convolutional coded and            | 156 |

|             | RCCC OFDM system                                                                  |     |

| Figure 6.20 | BER versus frame start time error for uncoded, convolutional coded and RCCC       | 157 |

|             | OFDM system                                                                       |     |

| Figure 6.21 | BER versus peak power clipping for uncoded, convolutional coded and RCCC          | 158 |

|             | OFDM system                                                                       |     |

| Figure 6.22 | BER versus channel noise of the RCCC OFDM system for different peak power         | 159 |

|             | clipping levels                                                                   |     |

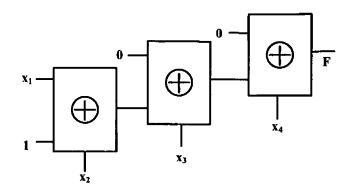

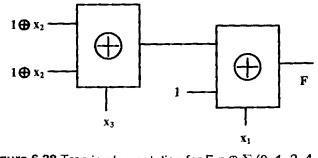

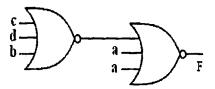

| Figure 6.23 | Exhaustive branched implementation for F = $\oplus \sum$ (13, 14)                 | 163 |

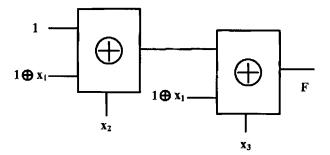

| Figure 6.24 | Tree implementation for F = $\oplus \sum$ (13, 14)                                | 164 |

| Figure 6.25 | Exhaustive branched implementation for F = $\oplus \Sigma$ (5, 6, 9, 10)          | 164 |

| Figure 6.26 | Tree implementation for F = $\oplus \Sigma$ (5, 6, 9, 10)                         | 165 |

| Figure 6.27 | Exhaustive branched implementation for F = $\oplus \sum$ (0, 1, 2, 4, 6)          | 165 |

| Figure 6.28 | Tree implementation for F = $\oplus \sum$ (0, 1, 2, 4, 6)                         | 165 |

| Figure 6.29 | Exhaustive branched and tree implementation for F = $\oplus \sum$ (0, 2, 3, 4, 5) | 166 |

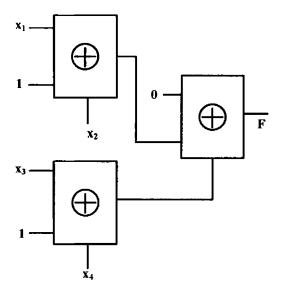

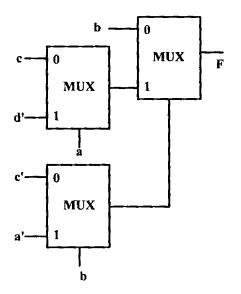

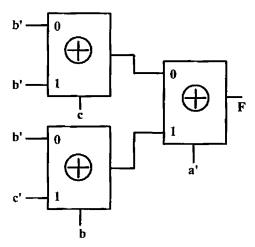

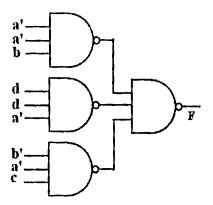

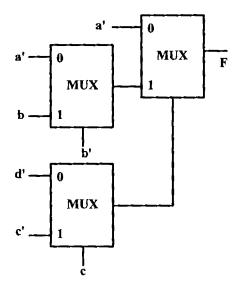

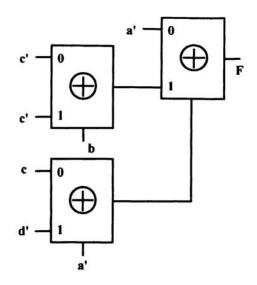

| Figure 6.30 | GA implementation for F = $\sum m$ (6, 7, 8, 12, 13, 14, 15)                      | 167 |

| Figure 6.31 | GA implementation for $F = \sum m (1, 2, 4)$                                      | 168 |

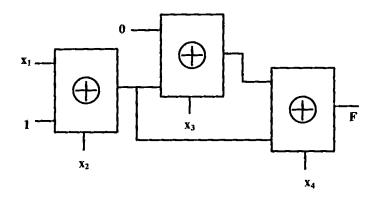

| Figure 6.32 | GA implementation for F = $\sum (1, 2, 3, 4, 5, 6, 7)$ using NOR gates            | 169 |

| Figure 6.33 | GA implementation for $F = \sum m (1, 2, 3, 4, 5, 6, 7)$ using NAND gates         | 169 |

| Figure 6.34 | GA implementation for $F = \sum m(1, 2, 3, 4, 5, 6, 7)$ using multiplexers        | 169 |

| 2           |                                                                                   |     |

| Figure 6.35 | GA implementation for F = $\sum$ m (1, 2, 3, 4, 5, 6, 7) using RM-ULMs        | 170 |

|-------------|-------------------------------------------------------------------------------|-----|

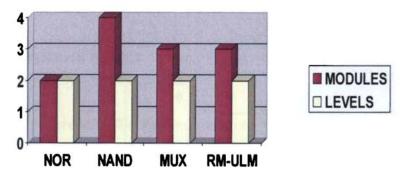

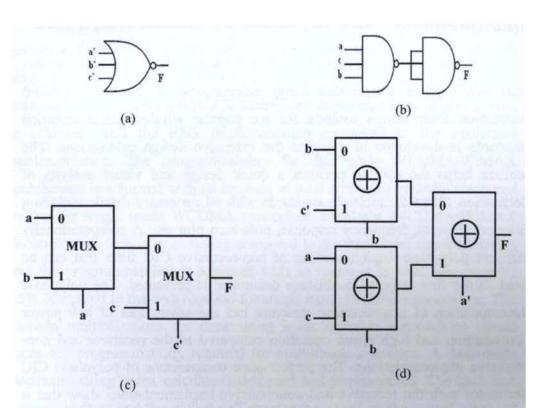

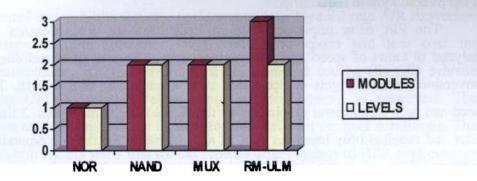

| Figure 6.36 | Comparison in terms of number of modules and levels required for implementing | 170 |

|             | $F = \sum m (1, 2, 3, 4, 5, 6, 7)$ with various ULMs                          |     |

| Figure 6.37 | GA implementation for F = $\Sigma m$ (7) using (a) NOR (b) NAND (c) MUX       | 171 |

|             | (d) RM-ULM                                                                    |     |

| Figure 6.38 | Comparison in terms of number of modules and levels required for implementing | 171 |

$F = \sum m$  (7) using NOR, NAND, MUX, and RM-ULM

viii

## LIST OF TABLES

| Table 1.1         | Milestones in wireless communication                                                       | 4           |

|-------------------|--------------------------------------------------------------------------------------------|-------------|

| Table 2.1         | Multi-standard specifications and decimation filter design parameters                      | 31          |

| Table 2.2         | Interference profile and C/N ratio                                                         | 32          |

| Table 3.1         | Standard specification and decimation filter design parameters for                         | 66          |

|                   | WCDMA/WiMAX transceiver                                                                    |             |

| Table 3.2         | Standard specification and decimation filter design parameters for                         | 70          |

|                   | WCDMA/WLANa transceiver                                                                    |             |

| Table 3.3         | Primitive roots for the selected moduli set                                                | 77          |

| Table 6.1         | Decimation filter implementation results for multiple standards                            | 130         |

| Table 6.2         | Total dynamic power consumption for CIC architectures                                      | 132         |

| Table 6.3         | Highest operating frequency for CIC architectures with $k = 4$ , $R = 64$ and $B_{in} = 4$ | 133         |

| Table 6.4         | Area requirement for CIC architectures                                                     | 133         |

| Table 6.5         | Critical path delay and area for 64 taps RNS FIR filter                                    | 138         |

| Table 6.6         | Critical path delay and area of reverse converter                                          | 139         |

| Table 6.7         | Critical path delay and area for 64 taps traditional FIR filter                            | 140         |

| Table 6.8         | Area and critical path delay of RNS decimation filter for WCDMA/WiMAX                      | 142         |

|                   | transceiver                                                                                |             |

| Table 6.9         | Area requirement for programmability                                                       | 143         |

| Table 6.10        | Area requirement for WCDMA/WiMAX decimation filter: Traditional Vs RNS                     | 143         |

| Table 6.11        | Area and critical path delay of RNS decimation filter for WCDMA/WLANa                      | 145         |

|                   | transceiver                                                                                |             |

| Table 6.12        | Area requirement for programmability                                                       | 146         |

| Table 6.13        | Area requirement for WCDMA/WLANa decimation filter: Traditional Vs RNS                     | 146         |

| <b>Table 6.14</b> | Area, critical path delay and dynamic power dissipation for RNS decimation filter          | 147         |

| Table 6.15        | Area requirement for programmability                                                       | 148         |

| <b>Table 6.16</b> | Area, critical path delay and dynamic power dissipation for traditional decimation         | 149         |

|                   | filter                                                                                     |             |

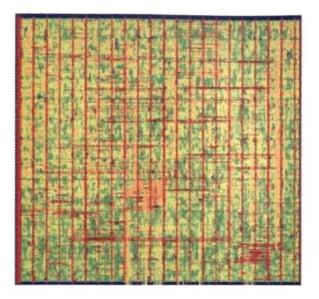

| Table 6.17        | Sigma-delta modulator complexity for A/R converters of various resolutions                 | 15 <b>1</b> |

| Table 6.18        | Decimation filter complexity for A/R converters with various resolutions                   | 152         |

| Table 6.19        | Performance comparison of A/R converters                                                   | 153         |

| Table 6.20        | PAPR for different peak power clipping                                                     | 159         |

| Table 6.21 | Number of test patterns for various adders in AND-OR and AND-XOR logic      | 162 |

|------------|-----------------------------------------------------------------------------|-----|

| Table 6.22 | Comparison in terms of delay and hardware for standard, tree and exhaustive | 166 |

branched implementations

## LIST OF ABBREVIATIONS

| A/R       | Analog-to-residue                                |

|-----------|--------------------------------------------------|

| ADC       | Analog-to-digital converter                      |

| ATPG      | Automatic test pattern generator                 |

| AWGN      | Additive white Gaussian noise                    |

| BER       | Bit error rate                                   |

| C/N ratio | Carrier to noise ratio                           |

| CF        | Correction factor                                |

| CIC       | Cascaded integrator comb                         |

| COFDM     | Coded orthogonal frequency division multiplexing |

| CPA       | Carry propagate adder                            |

| CR        | Clip compression ratio                           |

| CRT       | Chinese remainder theorem                        |

| CSA       | Carry save adder                                 |

| DAB/DVB   | Digital audio/video broadcasting                 |

| DAC       | Digital-to-analog converter                      |

| DECT      | Digital enhanced cordless telecommunication      |

| DFT       | Discrete Fourier transform                       |

| DR        | Dynamic range                                    |

| DS-CDMA   | Direct sequence - code division multiple access  |

| DSP       | Digital signal processing                        |

| EDGE      | Enhanced data rate for GSM environment           |

| ESOP      | Exclusive OR sum-of-products                     |

| FA        | Full adder                                       |

| FAN       | Fan-out oriented test generator                  |

| FEC       | Forward error correction                         |

| FFT       | Fast Fourier transform                           |

| FIR       | Finite impulse response                          |

| FPGA      | Field programmable gate array                    |

| FPRM      | Fixed polarity Reed-Muller                       |

| GA        | Genetic algorithm                                |

|           |                                                  |

| GF    | Galois field                                     |

|-------|--------------------------------------------------|

| GRM   | Generalized Reed-Muller                          |

| GSM   | Global system for mobile communication           |

| GUI   | Graphical user interface                         |

| GUIDE | Graphical user interface development environment |

| ICI   | Inter carrier interferences                      |

| IF    | Intermediate Frequency                           |

| IFFT  | Inverse fast Fourier transform                   |

| liR   | Infinite impulse response                        |

| IR    | Image reject                                     |

| ISI   | Inter symbol interferences                       |

| ITU   | International telecommunication union            |

| LO    | Local oscillator                                 |

| LUT   | Look up table                                    |

| LNA   | Low noise amplifier                              |

| MAC   | Multiply and accumulate unit                     |

| MASH  | Multistage noise shaping                         |

| MIMO  | Multiple input / multiple output                 |

| MRC   | Mixed radix conversion                           |

| MVL   | Multiple valued logic                            |

| NTF   | Noise transfer function                          |

| OFDM  | Orthogonal frequency division multiplexing       |

| OSR   | Oversampling ratio                               |

| PA    | Power amplifier                                  |

| PAPR  | Peak to average power ratio                      |

| PLA   | Programmable logic array                         |

| PPRM  | Positive polarity Reed-Muller                    |

| PSD   | Power spectral density                           |

| QAM   | Quadrature amplitude modulation                  |

| QPSK  | Quadrature phase shift keying                    |

| RCCC  | RRNS – Convolutional concatenated coding         |

| RF    | Radio frequency                                  |

| RM     | Reed-Muller                                     |

|--------|-------------------------------------------------|

| RM-ULM | Reed-Muller universal logic module              |

| RNS    | Residue number system                           |

| ROM    | Read only memory                                |

| RRNS   | Redundant residue number system                 |

| SD-ADC | Sigma-delta analog-to-digital converter         |

| SDR    | Software defined radio                          |

| SNR    | Signal to noise ratio                           |

| SRC    | Sampling rate conversion                        |

| STF    | Signal transfer function                        |

| ULM    | Universal logic module                          |

| VGA    | Variable gain amplifier                         |

| VLSI   | Very large scale integration                    |

| WCDMA  | Wideband code division multiple access          |

| WIF    | Wideband intermediate frequency                 |

| WIMAX  | Worldwide interoperability for microwave access |

| WLAN   | Wireless local area network                     |

# Chapter 1

# Introduction

This chapter serves to explore the history of wireless communication and the important milestones in its evolution. Radio Frequency (RF) receiver architectures suitable for high integration and multi-standard capability are presented. The need for Sigma-Delta analog-to-digital converter for multi-standard architectures addressing the various dynamic range requirements and sampling rates is discussed. The basic concepts of a sigma-delta modulator that achieves high resolution and signal to noise ratio in the baseband are also presented.

## **1.1** History of Wireless Communication

Telecommunication is defined by the International Telecommunication Union (ITU) as the transmission, emission or reception of any signs, signals or messages by electromagnetic systems. The demonstration of electrical telegraphy by Joseph Henry and Samuel F.B. Morse in 1832 followed shortly after the discovery of electromagnetism by Hans Christian Oersted and Andre-Marie Ampere early in the 1820's. In 1864 James Clerk Maxwell proved the existence of electromagnetic waves and postulated wireless propagation. This was verified and demonstrated by Heinrich Hertz in 1887. Guglielmo Marconi started experiments with the radio-telegraph shortly thereafter, and was awarded patent for wireless telegraph system in 1897. In mid-December 1901, he startled the world with transatlantic transmission [Palma, 2001]. In 1876, Alexander Graham Bell patented the telephone. The invention of the diode by Fleming in 1904 and the triode by Lee de Forest in 1906 led to the rapid development of long-distance radio telephony. The invention of the transistor by Bardeen, Braittain and Shockley that later led to the development of integrated circuits, paved the way for miniaturisation of electronic systems.

Wireless communication has developed into a key element of modern society. The developments in satellite transmission, radio and television broadcasting, and the new generation mobile systems have revolutionized global communication. The milestones in the evolution of wireless communication are listed in Table 1.1. The advances in micro-electronic circuits have recently undergone rapid development that made mobile and personal communication systems feasible. The critical attributes of such systems include high speed to transmit information in real time, world wide coverage, reliability, cost and security.

| 1921                                                                                   | Police car dispatch radios installed in Detroit                                                             |  |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| 1930s                                                                                  | Mobile transmitters developed; radio equipment occupied most of police car trunk                            |  |

| 1935                                                                                   | Frequency modulation (FM) demonstrated by Armstrong                                                         |  |

| 1946                                                                                   | First interconnection of mobile users to Public Switched Telephone Network (PSTN)                           |  |

| 1947                                                                                   | The advent of the cellular concept by D. H. Ring of AT&T Bell Laboratories                                  |  |

| 1949                                                                                   | FCC (Federal Communications Commission) recognizes mobile radio as new class of                             |  |

|                                                                                        | service                                                                                                     |  |

| 1960s                                                                                  | Improved Mobile Telephone Service (IMTS) introduced; supports full-duplex, auto                             |  |

|                                                                                        | dial, auto trunking                                                                                         |  |

| 1974                                                                                   | FCC allocates 40 MHz for cellular telephony                                                                 |  |

| Analog Cellular Age: first-generation (1G) for voice-only service                      |                                                                                                             |  |

| 1979                                                                                   | NTT (Nippon Telegraph and Telephone) Japan deploys first cellular communication                             |  |

|                                                                                        | system                                                                                                      |  |

| 1981                                                                                   | Commercial operation of NMT450 (Nordic Mobile Telephone – 450 MHz band)                                     |  |

| 1983                                                                                   | AMPS (Advanced Mobile Phone System) deployed in US in 900 MHz band: supports                                |  |

| 1000                                                                                   | 666 duplex channels                                                                                         |  |

| 1986                                                                                   | NMT900 system introduced in Scandinavia                                                                     |  |

| 1988                                                                                   | TACS (Total Access Communication System) introduced in UK and Japan                                         |  |

| Digital Cellular Age: Second-generation (2G) for digital voice and data communications |                                                                                                             |  |

| 1991                                                                                   | First GSM (Global System for Mobile Communications) network, Radiolinja in Finland was officially opened    |  |

| 1992                                                                                   | All major European operators start commercial operation of GSM networks                                     |  |

| 1993                                                                                   | GSM1800 system in commercial operation in UK                                                                |  |

| 1993                                                                                   | IS-95 CDMA(Interim Standard-95 Code Division Multiple Access) standard finalised                            |  |

| High Speed Cellular Age: Third-generation (3G) and higher for more advanced mobile     |                                                                                                             |  |

|                                                                                        | and services such as Internet and wireless access                                                           |  |

| 1999                                                                                   | Finland gave out the world's first 3G mobile technology licenses                                            |  |

| 2000s                                                                                  | First commercial GPRS and cdma2000 networks launched                                                        |  |

| 2001                                                                                   | Ericsson and Vodafone UK claim to have made the world's first WCDMA                                         |  |

|                                                                                        | (Wideband-CDMA) voice call over commercial network. Nokia and AT&T Wireless                                 |  |

|                                                                                        | complete first live 3G EDGE (Enhanced Data rate for GSM Evolution) call.                                    |  |

| 2002                                                                                   | Qualcomm announces world's first Bluetooth WCDMA (UMTS) and GSM Voice                                       |  |

|                                                                                        | Calls                                                                                                       |  |

| 2003                                                                                   | LG introduced the world's first dual band, dual mode phone for both CDMA and                                |  |

|                                                                                        | WCDMA                                                                                                       |  |

| 2004                                                                                   | Nortel Networks has completed the industry's first 3G partnership project (3GPP)                            |  |

| 1                                                                                      | compliant UMTS (Universal Mobile Telecommunication Systems)Assisted Global                                  |  |

| 2005                                                                                   | Positioning System (A-GPS) calls at 2100 and 1900 MHz                                                       |  |

| 2005                                                                                   | Ericsson demonstrates 9 Mbps with WCDMA, HSDPA (High-Speed Downlink<br>Backet Access) phase 2               |  |

| 2006                                                                                   | Packet Access) phase 2<br>Ericsson is the first to complete WCDMA calls on all 3GPP-defined frequency bands |  |

| 2008                                                                                   | 4G Technology beginning to shape up based on OFDM (Orthogonal Frequency                                     |  |

| 2007                                                                                   | Division Multiplexing) and aiming at 100 Mbps for wide area mobile applications.                            |  |

| 2008                                                                                   | Aims to launch WiMAX network offering 185 million subscribers 4G wireless data                              |  |

|                                                                                        | speeds up to 5 times faster than current wireless networks.                                                 |  |

|                                                                                        |                                                                                                             |  |

Table 1.1 Milestones in wireless communication

\_\_\_\_

## **1.2** Wireless System Developments

The Fourth Generation (4G) wireless networks aim to support global roaming across multiple wireless and mobile networks. Technologies employed by 4G include software defined radio (SDR) receivers, orthogonal frequency division multiplexing (OFDM) and multiple input/multiple output (MIMO) to attain reconfigurability and high data rate transmission. The recent advances in device scaling and integration together with the increasing demand for more services in portable communication favors the development of multi-mode transceivers [Soudris et al., 2000]. Reconfigurable wireless system is a new wireless technology that has great research potential and market interest. The trend for multi-mode support and flexible design increases the digital signal processing (DSP) portion of the transceiver. This implies moving the DSP more close to the front-end by placing analog-todigital converter close to the antenna.

Sigma-delta analog-to-digital converters (SD-ADCs) are widely used in multi-standard transceivers to adapt to the requirements of different standards. The SD-ADCs are promising candidates because of its readiness to reconfigure by changing the oversampling ratio, loop filter coefficients, loop filter order and number of quantizer bits. The most common architectures of Radio Frequency (RF) receivers with an emphasis on multi-standard capability and the principles of sigma-delta converter are explained in the following Sections 1.3 and 1.4.

## **1.3** Conventional RF Receiver Architectures

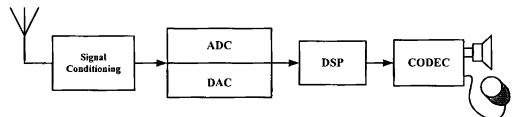

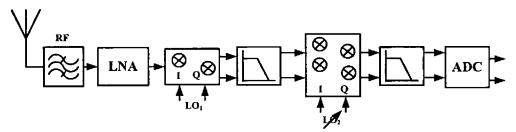

The general block diagram for an RF transceiver is shown in Figure 1.1. The incoming RF signal from the antenna is fed to the signal conditioning

block. The analog signal conditioning block performs frequency translation, amplification and filtering. Then it is digitized by an analog-to-digital converter (ADC). Sigma-delta ADCs are widely used in wireless communication transceivers as it provides high resolution and wide dynamic range. The DSP block performs further processing of the signal in digital domain. The sub-sections 1.3.1 - 1.3.4 describe the various RF receiver architectures with emphasis on its capability for high level of integration and multi-standard operation [Barrett, 1997].

Figure 1.1 Block diagram of a RF transceiver

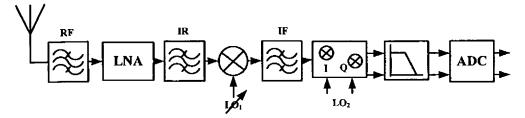

### 1.3.1 Superheterodyne Receiver

The traditional superheterodyne receiver architecture is shown in Figure 1.2. The received signal is passed through an RF filter and a low noise amplifier (LNA) that determines the receiver sensitivity. The signal is then passed through an image rejection (IR) filter that removes any image frequency signal present. The incoming signal frequency is translated to an intermediate frequency (IF) using a mixer and local oscillator. The IF is assigned a suitable high value to get adequate image rejection. The first local oscillator (LO<sub>1</sub>) is tuned to select the desired channel so that the signal is centred on the IF after mixing. The IF bandpass filter passes the desired signal rejecting the interference signals. The amplified IF signal is given to the second local oscillator (LO<sub>2</sub>) to split it into in-phase (I) and quadrature-phase

(Q) baseband components. This is followed by an antialiasing filter and analog-to-digital converter. Since the RF filter, IR filter and IF filter are offchip filters that are specific to a particular standard, this architecture is not suitable for high integration and multi-standard operation.

Figure 1.2 Superheterodyne receiver

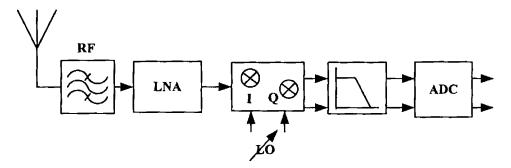

#### **1.3.2 Direct Conversion Homodyne Receiver**

The direct conversion homodyne receiver architecture is shown in Figure 1.3. The incoming signal after pre-filtering and amplification is directly translated to the baseband frequency without any IF. Hence it is also called a zero-IF receiver. The local oscillator is tuned to the centre frequency of the desired signal. The desired signal in-phase and quadrature-phase components are filtered via an on-chip lowpass filter and are digitized by ADC for further processing. As the received RF signal is directly translated to baseband, it does not suffer from image signal interferences. This eliminates the need for off-chip image reject filter. Also, it can be programmed for a multi-standard operation by tuning the local oscillator to select different standards. So the direct conversion receiver is suitable for higher integration and multi-standard operation. On the other hand, careful design considerations are required to control the DC offset and flicker noise created at the output of the mixer. The direct conversion homodyne receiver is the receiver architecture considered for analysis through out this research work.

Figure 1.3 Direct conversion homodyne receiver

#### 1.3.3 Low IF Receiver

The low IF receiver architecture is shown in Figure 1.4. In this topology, the incoming signal is translated to a suitably low IF, avoiding the DC offset and flicker noise associated with direct conversion. A low IF onchip bandpass filter is used to perform baseband channel selection. Hence this architecture offers high level of integration. But it is not attractive for wide bandwidth standards, as the power dissipation in the bandpass filter and ADC becomes intensive. So, the low IF receiver has only limited multi-standard capability.

Figure 1.4 Low IF receiver

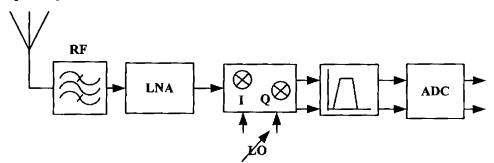

### 1.3.4 Wideband IF Double Conversion Receiver

The wideband IF (WIF) double conversion receiver architecture is shown in Figure 1.5. This architecture combines the strength of superheterodyne and direct conversion receivers through a two-stage frequency translation process. The first mixer mixes the RF signal with a fixed LO signal to produce IF which is then filtered by a lowpass filter to remove the harmonics and high frequency noise. The second mixer mixes this signal with variable LO signal to baseband, centring the desired channel at DC. The channel select filtering is performed at baseband with a programmable lowpass filter, making it suitable for multi-standard operation. This architecture also offers a high level of integration, as the off-chip IF and IR filters are eliminated.

Figure 1.5 Wideband IF double conversion receiver

## 1.4 Analog-to-Digital Converters

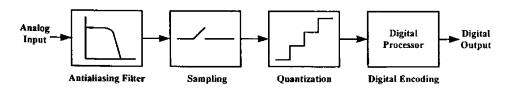

The process of converting an analog signal to digital representation encompasses sampling of analog waveform in time and quantizing it in amplitude [Rabii and Wooley, 1998]. The minimum rate at which the signal can be sampled is governed by its bandwidth. The block diagram of an ADC is shown in Figure 1.6.

Figure 1.6 Block diagram of analog-to-digital converter

The antialiasing filter is used to limit the bandwidth of the analog input to less than half of the sampling frequency. This ensures that the sampling process will not alias the out-of-band signals back into the baseband of the ADC. The width of the transition band of the antialiasing filter increases with the sampling rate, thereby decreasing the complexity of the filter. The quantized signal is digitally encoded based on the resolution which in turn dictates the quantization error. The ADCs are classified as Nyquist rate ADCs and oversampling ADCs based on the rate at which the signal is sampled relative to the signal bandwidth.

### 1.4.1 Nyquist Rate Analog-to-Digital Converters

Nyquist rate ADCs sample the signal at approximately twice the signal bandwidth, which is the minimum rate required for reconstruction of the signal according to Nyquist theorem. Such converters are used in data conversion systems where the conversion process is constrained by the bandwidth limitations of the implementation technology. Nyquist rate converters include parallel flash converters, successive approximation converters, counting or ramp converters etc. It generally requires operations such as comparison, amplification or subtraction to be performed at the overall precision of the converter. This translates into the need for precise component matching which limits the Nyquist rate converters to about 10 to 12-bits of resolution. So, alternate techniques are to be used for high resolution applications.

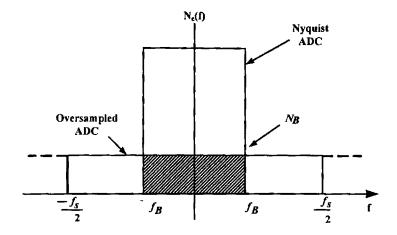

## 1.4.2 Oversampling Analog-to-Digital Converters

Oversampling ADCs sample the analog input at a rate much higher than the Nyquist rate. The ratio of sampling rate to the Nyquist rate is called the oversampling ratio. Oversampling ADCs exchange resolution in time for resolution in amplitude [Allen and Holberg, 2002]. Here each output is produced from a sequence of coarsely quantized input samples, whereas in Nyquist rate converters each digital word is obtained from an accurately sampled single sample of input. In oversampling ADCs the analog part is simple and do not require stringent component matching by performing most of the conversion process in digital domain. Hence these converters are suitable for high resolution implementations and today's VLSI technology tailored towards high speed and high density digital circuits. Oversampling converter relaxes the requirements of antialiasing filter. Another advantage is that they do not require a sample and hold circuit at the input.

Oversampling ADCs are classified into three main groups as straightoversampling ADCs, predictive ADCs and noise shaping ADCs. Straightoversampling ADCs exploit the fact that quantization noise is equally distributed over the entire frequency range, from DC to half the sampling frequency. So quantization noise power per frequency is reduced as shown in Figure 1.7. The shaded portion shows the baseband noise power  $(N_B)$  for oversampling ADC. Overall resolution is improved by removing the out-ofband noise by a digital filter. Predictive and noise shaping ADCs utilize oversampling and noise shaping concepts to attain a more efficient accuracyspeed trade off. Noise shaping is performed by placing the quantizer in a feedback loop in conjunction with a loop filter. In predictive ADCs loop filter is placed in the feedback path, and both signal and quantization noise spectra are shaped. In noise shaping ADCs, also called sigma-delta ADCs (SD-ADCs), the loop filter is placed in the feedforward path. Here, only the noise spectrum is shaped preserving the signal spectrum.

Figure 1.7 Baseband quantization noise power

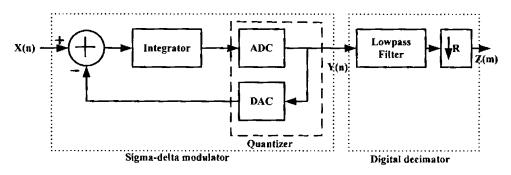

#### 1.4.2.1 Sigma-Delta Analog-to-Digital Converter

The SD-ADC is the most widely used oversampling ADC as it is more robust against circuit imperfections. It consists of an analog sigma-delta modulator part and a digital decimator part. A simple first order sigma-delta ADC is depicted in Figure 1.8. The first order sigma-delta ( $\sum \Delta$ ) modulator consists of an integrator and a coarse quantizer placed in a feedback loop. The quantizer is realized as either a one-bit comparator or a multi-bit quantizer.

Figure 1.8 Block diagram of first order sigma-delta ADC

When the integrator output is positive, quantizer feedbacks a positive signal which is subtracted from the input signal. This moves the integrator output in the negative direction. Similarly, when the integrator output is negative, the quanizer feedbacks a negative signal that is added at the input to move integrator output in the positive direction. Hence, the integrator accumulates the difference between input and quantizer output, and maintains the integrator output around zero. A zero integrator output implies that the difference between input and quantizer output is zero. In the sampled data model of modulator, quantization is represented as an additive error q, defined as the difference between the modulator output y and the quantizer input v. The input-output relationship of modulator as a difference equation is given in (1.1). The corresponding z-transform is given (1.2).

$$y[nT_s] = x[(n-1)T_s] + q[nT_s] - q[(n-1)T_s]$$

(1.1)

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})Q(z)$$

(1.2)

From (1.2), the signal transfer function (STF) is  $z^{-1}$  which represents unit delay and the noise transfer function (NTF) is  $(1-z^{-1})$  which represents a highpass characteristics. Hence the noise is shaped in such a way that the highpass nature allows noise suppression at low frequencies. This results in high signal to noise ratio (SNR) in the baseband. In general,  $L^{th}$  order noise shaping is achieved by placing L integrators in the forward path of the modulator. The noise transfer function becomes  $(1-z^{-1})^{L}$ . As the order of the modulator L increases, the baseband noise power decreases as shown in Figure 1.9. The modulator is followed by a digital decimation filter which removes the out-of-band noise and reconstructs the signal back at Nyquist rate. While the simple analog part of the ADC generally determines the resolution, the digital part occupies most of the die area and consumes much power. Hence, the design techniques that can reduce the die area and dynamic power consumption draw a great deal of research interest.

Figure 1.9 Noise shaping in sigma-delta modulators

## 1.5 Layout of the Thesis

The layout of the thesis is as follows: Chapter 2 presents a decimation filter design toolbox developed in MATLAB for six popular wireless standards, namely GSM, WCDMA, WLANa, WLANb, WLANg and WiMAX. The toolbox enables the communication system designer to perform a quick visual analysis of the filter performance without doing the complicated design calculations. A polyphase implementation of the non-recursive comb decimator for high speed operation that can be used as the first stage of a multistage decimator is also presented.

Chapter 3 illustrates the use of Residue Number System (RNS) for the high speed and area efficient implementation of digital filters. Dual-mode RNS based decimation filters reconfigurable for WCDMA/WiMAX and WCDMA/WLAN standards are designed and implemented. Modulo multipliers based on index calculus approach are used for increased programmability needed in multi-standard operation. A dual-mode decimator programmable for WCDMA/WLAN standards is designed using index calculus approach.

Chapter 4 introduces a novel parallel analog-to-residue converter based on sigma-delta converter for high resolution. An OFDM based communication system that explores the error detection and correction properties of Redundant Residue Number System (RRNS) is presented. The improvements in system performance obtained through the use of RRNS-Convolutional Concatenated Coding (RCCC) scheme for forward error correction under different operating conditions are also shown.

Chapter 5 describes easily testable circuit design using Reed-Muller (RM) logic. An exhaustive branching algorithm for implementing logic functions using Reed-Muller Universal Logic Modules (RM-ULMs) is presented. Genetic programming approach to realize logic functions using a particular ULM that implements the function using minimum number of modules and levels is also presented.

Chapter 6 presents the simulation results of various reconfigurable architectures and circuits described in Chapters 2, 3, 4 and 5. The performances of the new systems are compared with that of existing systems and the results are tabulated.

Chapter 7 concludes the thesis by drawing the conclusions from the results, and suggests possible extensions of the research work for further investigation. References are provided following this chapter along with the 'List of Publications' of the author.

# Chapter 2

# **Decimation Filter Design: A Toolbox Approach**

A multi-standard decimation filter design often involves extensive system level analysis and architectural partitioning, typically requiring extensive calculations. This chapter describes a multistage decimation filter design tool developed in MATLAB<sup>\*</sup> using Graphical User Interface Development Environment (GUIDE) for visual analysis. The toolbox is designed for six popular wireless communication standards consisting of GSM, WCDMA, WLANa, WLANb, WLANg and WiMAX.

This chapter also presents a computationally efficient polyphase implementation of non-recursive cascaded integrator comb (CIC) decimator for Sigma-Delta Converters. This polyphase implementation offers high speed operation and low power consumption for the first stage of a multistage decimator.

## 2.1 Decimation Filter Design Considerations